[HFR] Actu : Samsung présente sa SRAM 10nm

Actu : Samsung présente sa SRAM 10nm [HFR] - HFR - Hardware

Marsh Posté le 05-02-2016 à 15:28:27 2

Si j'ai bien compris la SRAM c'est ce qui sert de cache dans les CPU / GPU ?

Marsh Posté le 05-02-2016 à 15:53:11 2

Oui.

C'est plus facile à interfacer que la DRAM, c'était très utilisé comme RAM principale dans les micro-ordinateurs des années 70, et encore aujourd'hui dans les micro-contrôleurs (exemple : l'ordinateur dans un four micro-ondes)

Message édité par blazkowicz le 05-02-2016 à 15:53:25

Marsh Posté le 05-02-2016 à 16:20:04 0

Il y a t il une partie du transistor qui a un rapport avec le nom de la gravure ou pas du tout ?

Marsh Posté le 05-02-2016 à 19:10:08 1

La sram c'est génial, tu tappes une adresse et tu reçois la data. Beaucoup plus simple que la dram.

Mais très couteuse.

Marsh Posté le 05-02-2016 à 21:04:00 2

Comparer les surface, sans comparer les performances de consommation, de vitesse, ni même de tarif, ça sert juste à rien. C'est une façon d'exciter les économistes c'est tout.

Et pire encore, on ne cite même pas le nom des process de façon spécifique.

Juste pour dire, intel doit avoir une demi-douzaine de process 14nm, et Samsung certainement aussi un nombre non négligeable.

Je n'imagine pas du tout comparer de la sram sur du 28nm de chez ST en FDSOI UTBB contre des transistors finfet d'intel en 14nm High power.

Un peu de bon sens svp.

Marsh Posté le 05-02-2016 à 21:05:48 1

| lulunico06 a écrit : Il y a t il une partie du transistor qui a un rapport avec le nom de la gravure ou pas du tout ? |

Pas vraiment. Ca depend de chaque process. Ces dernières années c'était a peu près la moitié du pitch de la couche métallique la plus basse (qui sert aux interconnexions). Référencé comme "1/2 pitch M1" dans les roadmaps.

Il y a un comité pour donner les grandes lignes des process, l'ITRS, qui publie des roadmaps. Un PDF ici (a renommer...) : http://ieuvi.org/TWG/Mask/2013/MTG [...] nk_Goodwin

Slide 14, section MPU/Logic.

Cette présentation est bien sinon sur la question de pourquoi les challenges/changements de nomenclatures : http://www.ewh.ieee.org/r6/scv/eds [...] -Paolo.pdf

Marsh Posté le 05-02-2016 à 23:17:16 1

| barbare128 a écrit : Comparer les surface, sans comparer les performances de consommation, de vitesse, ni même de tarif, ça sert juste à rien. C'est une façon d'exciter les économistes c'est tout. Et pire encore, on ne cite même pas le nom des process de façon spécifique. Juste pour dire, intel doit avoir une demi-douzaine de process 14nm, et Samsung certainement aussi un nombre non négligeable. Je n'imagine pas du tout comparer de la sram sur du 28nm de chez ST en FDSOI UTBB contre des transistors finfet d'intel en 14nm High power. Un peu de bon sens svp. |

Une demi-douzaine, je veux bien une source, idem pour Samsung qui n'a à ma connaissance que deux process 14nm, et encore le second LPP étant destiné à remplacé le premier LPE. TSMC va avoir deux process 16nm à terme (FF+ et FFC).

Pour le reste, je cite "la taille de la SRAM n'étant pas non plus le seul facteur à prendre en compte" ... donc pas la peine de s'exciter ![]() Reste que la taille est aussi un paramètre, d'ailleurs le ratio de taille entre l'A9 d'Apple en version TSMC ou Samsung correspond quasi au ratio entre les deux SRAM annoncées par les fondeurs.

Reste que la taille est aussi un paramètre, d'ailleurs le ratio de taille entre l'A9 d'Apple en version TSMC ou Samsung correspond quasi au ratio entre les deux SRAM annoncées par les fondeurs.

Sinon le jour ou tu a accès aux tarifs Intel / Samsung / TSMC pour un wafer n'hésite pas à nous les donner ![]()

Message édité par Marc le 05-02-2016 à 23:21:26

Marsh Posté le 06-02-2016 à 00:41:45 1

on a jamais les tarifs des wafers meme "finaux" ?

Message édité par cyrille_0088 le 06-02-2016 à 00:44:58

Marsh Posté le 06-02-2016 à 05:02:43 1

je ne crois pas que barbare critique Hfr, mais plutot ce que dit Samsung...

Certes, il n'y a que 2 process 16/14nm chez chaque fondeur disponible pour le clients, mais combien en interne (pour le dev etc)?

On peut s'attendre a ce que ce type de record soient realisé sur des process qui ne soient pas disponible pour les clients...

Sinon, une autre question, plus personne ne fait du SOI (meme PD- partially depleted?).

Marsh Posté le 06-02-2016 à 05:04:07 1

Ça serait sûrement nuisible aux pratique commerciales d'Intel notamment surtout que dans le domaine pro c'est l'acheteur qui choisit le prix de ton bien

Marsh Posté le 06-02-2016 à 05:25:49 0

Remarque à deux balles ( sûrement fausse ) : Le process on en a aucune idée puisque ceux officiels ce sont ( chez Samsung ) le 14nm LPP / LPE Finfet et donc graver une puce en 10nm avec un process en 14nm c'est impossible ![]()

Marsh Posté le 06-02-2016 à 08:34:50 2

Marc a écrit :

Une demi-douzaine, je veux bien une source, idem pour Samsung qui n'a à ma connaissance que deux process 14nm, et encore le second LPP étant destiné à remplacé le premier LPE. TSMC va avoir deux process 16nm à terme (FF+ et FFC). |

En ce qui concerne les différents process, tu as les process de base et les variantes de ces process.

En général peu médiatisé, voir pas du tout. Ex pour la même appelation de process 28nm d'un fondeur connu, j'en connais sûr 3 variantes, et qui sont électriquement très différents, et aussi au niveau des performances. Je sais qu'il y en a d'autres que je ne connais pas sur ce fondeur. Si je le sais, c'est que j'ai bossé sur ces DKs un temps.

Par ailleurs rien n'empêche les clients des fab de demander des process particulier pour tel ou composants.

Un process c'est comme une recette de cuisine. ( C'est comme ça que c'est perçu dans le milieu ).

Et un client, ( s'il a les moyens ) il peut demander, je veux plus d'oeufs ou de farine.

Un de mes projets de recherche était justement sur un process avec une recette dédié pour ce composant.

Et je rejoint bgx, je ne critique pas votre boulot, juste que la communication des fondeurs et des chercheurs est un peu trop centré chiffres types "figure of merit" et qu'au fond plus le temps passe, plus ces graphiques et chiffres ne veulent plus rien dire à part pour les investisseurs.

Marsh Posté le 06-02-2016 à 13:34:37 2

| barbare128 a écrit : |

Non, Intel est justement le roi de la monoculture côté process. Du plus gros Xeon au plus piètre Core M, en 14nm, c'est le même process (P1272) qu'Intel appelle "CPU". Avec toutes les conséquences que cela peut avoir évidemment.

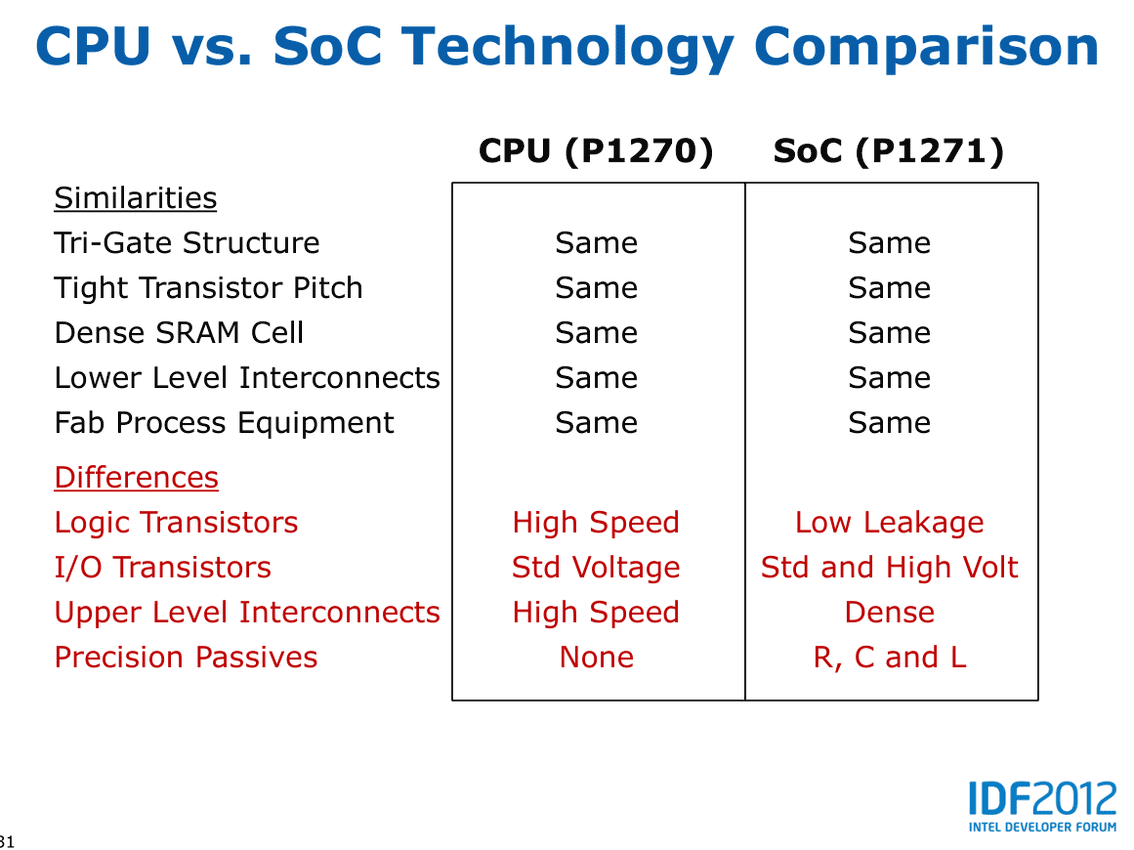

Intel ne dévie de sa stratégie que pour la très basse conso pour lequel ils se forcent à faire une variante "SoC" (P1273 en 14nm, P1271 en 22). Cf ce slide qui compare les deux process 22nm (P1270 CPU, et P1271 SoC) :

Malgré tout, les grandes lignes restent très proches, la SRAM (le sujet de la news) reste identique entre les deux process 22nm par exemple. La monoculture d'Intel a toujours été à la fois leur force et leur faiblesse (ils sont toujours obligés de faire fabriquer leurs modems chez TSMC par exemple faute de radio) mais ça n'est pas le débat.

| Citation : En ce qui concerne les différents process, tu as les process de base et les variantes de ces process. |

... ou est le rapport ?

L'annonce de Samsung porte sur le 10nm, un process bleeding edge en fin d'élaboration, on ne parle pas de 28 qui est dans un tout autre cycle d'exploitation.

Qui plus est, post 28, les fondeurs ont changé leur stratégie en se centrant sur un process principal dont les variantes marquent plus leur date de disponibilité qu'une différence de cible. En grande partie parce qu'ils ont un (ou deux) gros clients à très gros volumes à satisfaire avant les autres sur une cadence différente du reste de leurs clients. Le E du 14LPE de Samsung veut dire "Early". TSMC avait annoncé à la base la même stratégie avec un "16 FF" et un "16 FF+", même si en pratique on aura eu directement la version +. Les variantes existent bien entendu toujours a l'intérieur (ou autour, notamment pour toutes les technos packaging) des process mais en pratique aujourd'hui ce sont les clients gros volumes qui dictent le bleeding edge chez TSMC/Samsung. Les variantes n'arrivent que lorsque le process est ouvert aux autres clients, quand les gros sont passés à la suite. Et de la même manière que seuls Apple et Qualcomm ont exploité le 20nm chez TSMC (tout les autres ont "sauté" le 20 pour faire 28 et bientôt, un jour, promis, du 16), le 10 devrait suivre à peu près le même chemin d'après ce que l'on a entendu dans les conférences aux investisseurs de TSMC. Le prochain node "pour tour le monde" sera plus probablement le 7 chez TSMC si on lit entre les lignes leurs roadmaps.

Pour revenir au vrai sujet, les annonces de taille de SRAM sont un classique pour les nouveaux process et historiquement, les annonces autour de la 6T dense (un composant fondamental de base) donnent une assez bonne idée de la densité relative des différents process, indépendamment du fait que de nombreux autres paramètres rentrent en compte. Les cellules annoncées sont parfois utilisées, parfois pas (Intel par exemple présente souvent à l'ISSCC des densités un peu plus "optimales" que ce qu'ils utilisent en réalité contrairement a TSMC/Samsung, mais on le prend en compte lorsque l'on en parle). En pratique c'est l'un des meilleurs indicateurs publiques disponibles pour comparer les process bleeding edge dans l'utilisation qui nous intéresse (CPU/SoC) sur lesquels excessivement peu d'informations sont disponibles pour des raisons concurrentielles, évidemment.

C'est d'autant plus important d'en parler aujourd'hui avec la divergence de stratégie des fondeurs sur la manière de scaler leurs process, TSMC et Samsung choisissant de mutualiser une partie des couches metal pour deux nodes successifs (20 et 16, et probablement 10 et 7 même si ils ne l'ont pas encore dit clairement publiquement au delà du timing annoncé). Intel est plus "puriste" sur la densité (ce qui n'a rien a voir avec les performances, mais Intel optimise tout autour de la métrique densité), mais l'on a vu les retards que cela engendre par rapport à la concurrence, pour un avantage de performance pas forcément évident.

Message édité par C_Wiz le 06-02-2016 à 13:40:33

Marsh Posté le 07-02-2016 à 09:27:55 1

Ce slide est intéressant. Intel indique que les éléments structurels des transistors sont les même et que l'équipement est le même.

Cependant, leur "monoculture" est surtout lié au fait qu'ils se concentre sur des process type processeur, les process on va dire basique ou classique.

Intel ne travaille pas la RF, ni les process d'imagerie, ni d'autres process demandant des fabrications très particulières.

Et la ou il faut être attentif dans ce slide, c'est la ligne I/O transistors.

Cette ligne est importante. Il est indiqué que les sur les SOC les I/O peuvent être de tension plus importantes. Pour moi c'est ici évident que intel utilise une "recette" légèrement différente pour ces deux la.

Je doute que la couche de SIO2 soit de la même épaisseur sur tout le CPU et le SOC. Ce serait une réduction évidente de performances d'en mettre plus partout. Ils doivent peut-être masker et faire plusieurs épaisseurs pour le process soc.

Et le fait qu'intel présente ça sous forme de deux colonnes, c'est bien la preuve que le DK ( Design Kit ) est différent.

Effectivement, je considère que même sans différence de process, un DK différent, et suffisamment significatif pour être différent en pratique.

Marsh Posté le 07-02-2016 à 15:09:41 0

C_Wiz a écrit :

Pas vraiment. Ca depend de chaque process. Ces dernières années c'était a peu près la moitié du pitch de la couche métallique la plus basse (qui sert aux interconnexions). Référencé comme "1/2 pitch M1" dans les roadmaps. |

Merci pour ta réponse dommage le second lien ne marche pas.

Marsh Posté le 07-02-2016 à 17:40:14 0

| lulunico06 a écrit : |

Retesté a l'instant, il marche ici ?

Marsh Posté le 08-02-2016 à 14:06:31 0

Sinon un peu HS mais intéressant quand même : http://www.tomshardware.fr/article [...] 58497.html

Marsh Posté le 09-02-2016 à 08:35:47 0

Dans un même process il peut y avoir tellement d'options:

capactité mim, oxyde simple, double épaisseur, transistor de puissance, bipolaire, bipolaire haute tension etc.

En jouant avec les options (et le prix des masques associés!) on peut avoir plein de variantes au sens d'un même process. Certain process on plus de 50 masques, ça douille très vite.

Aux designers de choisir les options les plus utiles à leurs design sans plomber le prix d'un circuit.

Message édité par standalone le 09-02-2016 à 15:22:51

Marsh Posté le 10-02-2016 à 14:38:59 0

Quoi de plus parlant que l'area d'une bitcell Sram, surtout pour de la HD.

Marsh Posté le 10-02-2016 à 19:25:59 0

Chez Intel je vois bien où se retrouve leur SRAM, mais dans le cas de Samsung ? Surtout 16Mo, ça doit pas être utilisé dans des CPUs de téléphones.

---------------

New Technology is the name we give to stuff that doesn't work yet. Douglas Adams

Marsh Posté le 12-02-2016 à 11:00:20 0

| asmomo a écrit : Chez Intel je vois bien où se retrouve leur SRAM, mais dans le cas de Samsung ? Surtout 16Mo, ça doit pas être utilisé dans des CPUs de téléphones. |

Non il n'y a pas de SRAM... non non... ![]()

http://anandtech.com/show/8562/chipworks-a8

http://images.anandtech.com/doci/8 [...] blocks.png

Grosso modo tous les carrés à quadrillage régulier son de la SRAM:

- Caches CPU L1 I et D (pour chaque coeur),L2 et L3

- Write buffers/ victim caches

- plus les tags pour chaque cache de chaque coeur

- TLB L1 (pour chaque coeur) et L2

- Caches L1 et L2/ buffers dans le GPU

- Buffers SRAM énormes dans les contrôleurs SDRAM

- de la SRAM pour les interfaces BUS à l'intérieur du SOC

- Plein de blocs SRAM dispersés dans chaque périphérique du SOC (fifo/buffers etc...)

Les SOC de mobiles sont bourrés de bloc SRAM, ça prend un grosse partie du chip.

L'utilisation de la SRAM pour faire des concours de bŷthe n'est pas anodin. En plus c'est un motif simple et régulier.

Marsh Posté le 12-02-2016 à 21:39:49 0

OK mais c'est pas 16Mo. Maintenant si tu dis que c'est un die démo/technological preview, d'accord.

---------------

New Technology is the name we give to stuff that doesn't work yet. Douglas Adams

Sujets relatifs:

- WII sur ecran Samsung full HD

- [HFR] Actu : Pilotes AMD 16.1.1 Hotfix pour Tomb Raider

- avis sur msiz170 gaming pro + samsung 950 pro

- [HFR] Actu : OCZ lance le Trion 150

- [HFR] Actu : Excavator FM2+ et nouveaux ventirads AMD

- Clef USB 128 Go : Sandisk ou Samsung ?

- [HFR] Actu : L'AM3+ a droit au M.2 et l'USB 3.1 via 4 cartes mères

Marsh Posté le 05-02-2016 à 15:07:42 0

Lors de l'ISSCC, Samsung a été le seul a communiquer sur le 10nm via la présentation d'une puce de 16 Mo de SRAM gravée en 10nm FinFET de 75.6mm². Deux types de ...

Lire la suite ...

Message édité par Marc le 05-02-2016 à 22:49:04